# FMC 4 路干兆以太网模块 FL2121 用户手册

**Rev 1.0**

版权声明:

Copyright ©2012-2018 芯驿电子科技 (上海) 有限公司

公司网址:

Http://www.alinx.com.cn

技术论坛:

http://www.heijin.org

官方旗舰店:

http://alinx.jd.com

邮箱:

avic@alinx.com.cn

电话:

021-67676997

传真:

021-37737073

ALINX 微信公众号:

## 文档修订记录:

| 版本  | 时间         | 描述            |

|-----|------------|---------------|

| 1.0 | 2022/11/20 | First Release |

|     |            |               |

|     |            |               |

|     |            |               |

|     |            |               |

|     |            |               |

|     |            |               |

# 第一部分 FMC 高速以太网模块说明介绍

黑金 FMC 千兆以太网模块 FL2121 为 4 路 10/100/1000Mbps 自适应的以太网通信接口模块。 FMC 模块的千兆 PHY 芯片采用了 4 片景略半导体公司的JL2121 以太网 PHY 芯片,支持 10/100/1000 Mbps 网络传输速率。4 路网络接口采用常用的 RJ45 连接器跟外部网络连接和通信。

模块有一个标准的 LPC 的 FMC 接口,用于连接 FPGA 开发板, FMC 的连接器型号为: ASP 134604\_01

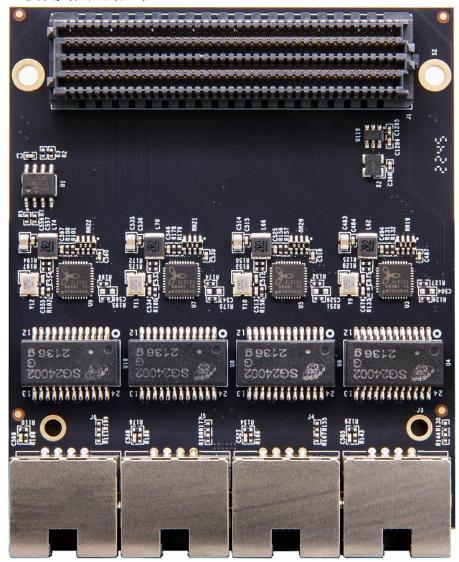

FL2121 模块实物照片如下:

FL2121 模块实物图

## 1.1 FL2121 模块的参数说明

以下为 FL2121 千兆以太网模块的详细参数:

➤ 干兆以太网芯片: 4 片 JL2121

➤ 网络接口: 4路 RJ45;

▶ 以太网通信速率: 支持 10/100/1000 Mbps;

▶ 通信方式: RGMII;

▶ 配置接口: MDIO 接口;

➤ 工作温度: -40°~85°;

## 1.2 FL2121 模块的结构图

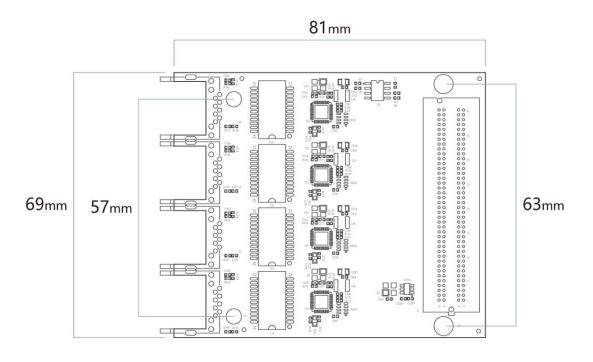

FL2121 千兆以太网模块尺寸结构图

# 第二部分 模块功能说明

# 2.1 FL2121 模块原理框图

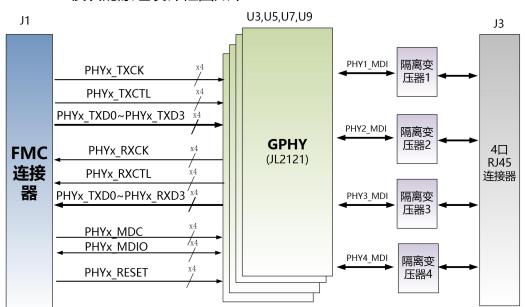

#### FL2121 模块的原理设计框图如下:

## 2.2 太网芯片

以太网芯片采用景略半导体的工业级以太网 GPHY 芯片(JL2121-N040I)为用户提供网络通信服务。PS 端的以太网 PHY 芯片是连接到 ZYNQ 的 PS 端 BANK502 的 MIO 接口上。PL 端的以太网 PHY 芯片是连接到 BANK66 的 IO 上。JL2121 芯片支持 10/100/1000 Mbps 网络传输速率,通过 RGMII 接口跟 MPSOC 系统的 MAC 层进行数据通信。JL2121D 支持MDI/MDX 自适应,各种速度自适应,Master/Slave 自适应,支持 MDIO 总线进行 PHY 的寄存器管理。

JL2121 上电会检测一些特定的 IO 的电平状态,从而确定自己的工作模式。 下表描述了 GPHY 芯片上电之后的默认设定信息。

| 配置 Pin 脚   | 说明                  | 配置值               |

|------------|---------------------|-------------------|

| RXD3_ADR0  | MDIO/MDC 模式的 PHY 地址 | PHY Address 为 001 |

| RXC_ADR1   |                     |                   |

| RXCTL_ADR2 |                     |                   |

| RXD1_TXDLY | TX 时钟 2ns 延时        | 延时                |

| RXD0_RXDLY | RX 时钟 2ns 延时        | 延时                |

GPHY 芯片默认配置值

当网络连接到干兆以太网时,MPSOC 和 PHY 芯片 JL2121 的数据传输时通过 RGMII 总线通信,传输时钟为 125Mhz,数据在时钟的上升沿和下降样采样。

当网络连接到百兆以太网时,MPSOC 和 PHY 芯片 JL2121 的数据传输时通过 RMII 总线通信,传输时钟为 25Mhz。数据在时钟的上升沿和下降样采样。

# 2.3 模块 FMC LPC 的引脚分配:

下面只列了电源和网络芯片接口的信号, GND 的信号没有列出, 具体用户可以参考原理图。

| Pin Number | Signal Name | Description       |

|------------|-------------|-------------------|

| C35        | +12V        | 12V 电源输入          |

| C37        | +12V        | 12V 电源输入          |

| D32        | +3. 3V      | 3. 3V 电源输入        |

| C34        | GAO         | EEPROM 地址位 0 位    |

| D35        | GA1         | EEPROM 地址位 1 位    |

| D11        | PHY1_MDC    | 以太网第一路 MDIO 管理时钟  |

| C11        | PHY1_MDIO   | 以太网第一路 MDIO 管理数据  |

| D12        | PHY1_RESET  | 以太网第一路复位信号        |

| G6         | PHY1_RXCK   | 以太网第一路 RGMII 接收时钟 |

| G7         | PHY1_RXCTL  | 以太网第一路接收数据有效信号    |

| H4         | REFCLK      | 50MHz 的参考时钟       |

| Н7         | PHY1_RXD0   | 以太网第一路接收数据 Bit0   |

| Н8         | PHY1_RXD1   | 以太网第一路接收数据 Bit1   |

| G9         | PHY1_RXD2   | 以太网第一路接收数据 Bit2   |

| G10        | PHY1_RXD3   | 以太网第一路接收数据 Bit3   |

| H11        | PHY1_TXCK   | 以太网第一路 RGMII 发送时钟 |

| H14        | PHY1_TXCTL  | 以太网第一路发送数据有效信号    |

| H10        | PHY1_TXD0   | 以太网第一路发送数据 Bit0   |

| G12        | PHY1_TXD1   | 以太网第一路发送数据 Bit1   |

| G13        | PHY1_TXD2   | 以太网第一路发送数据 Bit2   |

| H13        | PHY1_TXD3   | 以太网第一路发送数据 Bit3   |

| D18        | PHY2_MDC    | 以太网第二路 MDIO 管理时钟  |

| C19        | PHY2_MDIO   | 以太网第二路 MDIO 管理数据  |

| H20        | PHY2_RESET  | 以太网第二路复位信号        |

| D8         | PHY2_RXCK   | 以太网第二路 RGMII 接收时钟 |

| D9         | PHY2_RXCTL  | 以太网第二路接收数据有效信号    |

| C10        | PHY2_RXD0   | 以太网第二路接收数据 Bit0   |

| D14        | PHY2_RXD1   | 以太网第二路接收数据 Bit1   |

| C15        | PHY2_RXD2   | 以太网第二路接收数据 Bit2   |

| D15        | PHY2_RXD3   | 以太网第二路接收数据 Bit3   |

| H17        | PHY2_TXCK   | 以太网第二路 RGMII 发送时钟 |

| H19        | PHY2_TXCTL  | 以太网第二路发送数据有效信号    |

| G16        | PHY2_TXD0   | 以太网第二路发送数据 Bit0   |

| H16        | PHY2_TXD1   | 以太网第二路发送数据 Bit1   |

| G18        | PHY2_TXD2   | 以太网第二路发送数据 Bit2   |

| G19 | PHY2_TXD3  | 以太网第二路发送数据 Bit3   |

|-----|------------|-------------------|

| H28 | PHY3_MDC   | 以太网第三路 MDIO 管理时钟  |

| G28 | PHY3_MDIO  | 以太网第三路 MDIO 管理数据  |

| H29 | PHY3_RESET | 以太网第三路复位信号        |

| D20 | PHY3_RXCK  | 以太网第三路 RGMII 接收时钟 |

| G21 | PHY3_RXCTL | 以太网第三路接收数据有效信号    |

| G22 | PHY3_RXD0  | 以太网第三路接收数据 Bit0   |

| H22 | PHY3_RXD1  | 以太网第三路接收数据 Bit1   |

| D23 | PHY3_RXD2  | 以太网第三路接收数据 Bit2   |

| D24 | PHY3_RXD3  | 以太网第三路接收数据 Bit3   |

| H25 | PHY3_TXD3  | 以太网第三路发送数据 Bit3   |

| G27 | PHY3_TXCTL | 以太网第三路发送数据有效信号    |

| H23 | PHY3_TXD0  | 以太网第三路发送数据 Bit0   |

| G24 | PHY3_TXD1  | 以太网第三路发送数据 Bit1   |

| G25 | PHY3_TXD2  | 以太网第三路发送数据 Bit2   |

| H26 | PHY3_TXCK  | 以太网第三路 RGMII 发送时钟 |

| Н35 | PHY4_MDC   | 以太网第四路 MDIO 管理时钟  |

| Н37 | PHY4_MDIO  | 以太网第四路 MDIO 管理数据  |

| Н38 | PHY4_RESET | 以太网第四路复位信号        |

| C22 | PHY4_RXCK  | 以太网第四路 RGMII 接收时钟 |

| C23 | PHY4_RXCTL | 以太网第四路接收数据有效信号    |

| D26 | PHY4_RXD0  | 以太网第四路接收数据 Bit0   |

| C26 | PHY4_RXD1  | 以太网第四路接收数据 Bit1   |

| D27 | PHY4_RXD2  | 以太网第四路接收数据 Bit2   |

| C27 | PHY4_RXD3  | 以太网第四路接收数据 Bit3   |

| Н32 | PHY4_TXCK  | 以太网第四路 RGMII 发送时钟 |

| H34 | PHY4_TXCTL | 以太网第四路发送数据有效信号    |

| G31 | PHY4_TXD0  | 以太网第四路发送数据 Bit0   |

| Н31 | PHY4_TXD1  | 以太网第四路发送数据 Bit1   |

| G33 | PHY4_TXD2  | 以太网第四路发送数据 Bit2   |

| G34 | PHY4_TXD3  | 以太网第四路发送数据 Bit3   |

| C30 | SCL        | EEPROM 的 I2C 时钟   |

| C31 | SDA        | EEPROM 的 I2C 数据   |

| G39 | VADJ       | VADJ 电源输入         |

| H40 | VADJ       | VADJ 电源输入         |

# 第三部分 硬件连接和测试

FL2121 模块和 FPGA 开发板的硬件连接很简单,只要把 FMC 接口跟开发板的 FMC 接口对插就可以,然后用螺丝固定。以下为黑金 AX7325 开发板的和

#### FL2121 模块的硬件连接图:

## ▶ 准备工作

第一步: 首先确认一下自己 PC 的网卡是否是千兆网卡, 用户可以点击本地连接 查看,再用五类+或者六类网线连接开发板的网口和 PC 的网口。

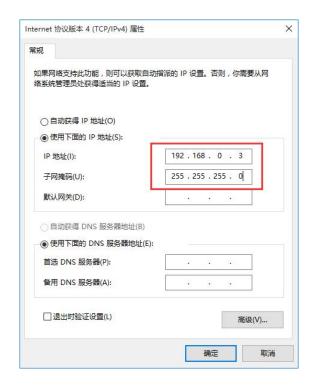

第二步: 修改 PC 的 IP 地址为 192.168.0.3。PC 的 IP Address 需要和程序中 mac test.v 中设置一致,不然网络调试助手会接收不到开发板发送的 UDP 数据 包。

- 48'h00\_0a\_35\_01\_fe\_c0) 8'h80), 32'hc0a80002). .TTL

.source\_ip\_addr

.destination\_ip\_addr

.udp\_send\_source\_port

.udp\_send\_destination\_port

第三步(可选):安装 Wireshark 是为了方便用户网络通信的调试,安装光盘的 TOOL 目录下的网络抓包工具 Wireshark, 我们在实验的时候可以用这工具来查看 PC 网口发送的数据和接收到的数据的详细信息。

# > 以太网通信测试

第一步: 烧写 bit 文件到 FPGA 芯片。

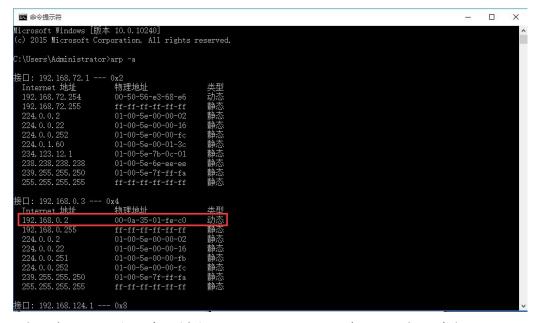

第二步:按下开发板的 KEY2 按键,之后打开 CMD 窗口,输入 arp -a 查看 ARP

绑定结果,可以看到开发板的 IP 地址和 MAC 地址已经缓存。

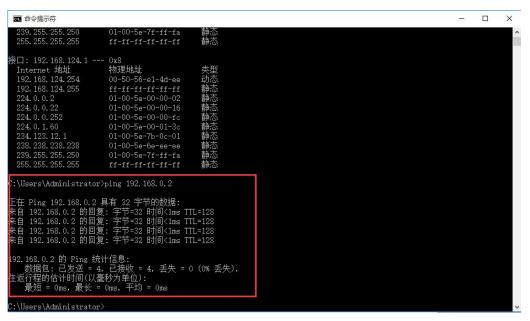

第三步:在 CMD 窗口中,输入 ping 192.168.0.2 查看 PC 与开发板是否 ping 通。

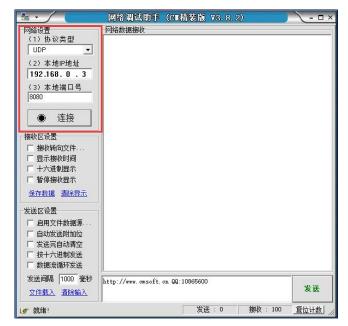

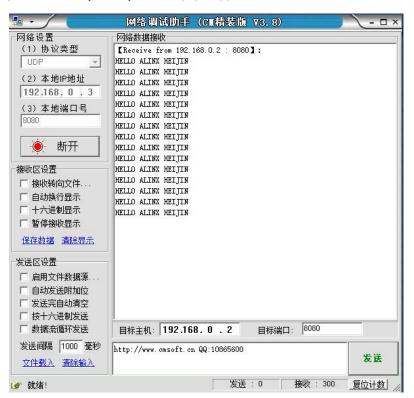

第四步: 打开 TOOL 目录下的网络调试助手并设置参数如下,再按连接按钮(这里的本地的 IP 地址为 PC 的 IP Address,本地端口需要跟 FPGA 程序中的一致,为8080)。

这时网络数据接收窗口会显示 FPGA 发给 PC 的以太网数据包"Hello ALINX HEIJIN"目标主机的 IP 地址需要和 FPGA 程序中的 IP 地址一致,目标端口号也需要和 FPGA 程序的一致(8080)。如下图网络显示:

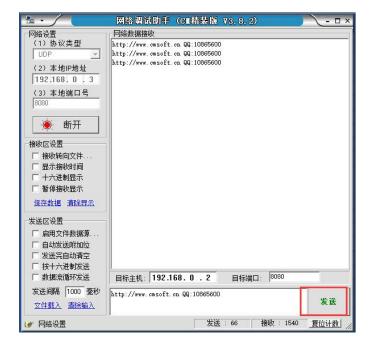

第五步:再在网络调试助手的发送窗口发送一大串字符,在网络的数据接收窗口我们可以看到从 FPGA 返回的数据也变成刚发送的字符串。

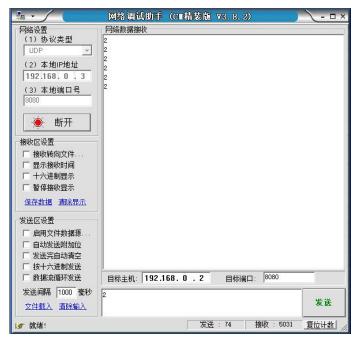

也可以发送较少字符, 低于 46 字节, FPGA 程序会自动补充至 46 字节, 如下图:

第六步:这一步对用户来讲是可选的,用户如果想查看更多数据包传输的信息,可以使用网络抓包工具 Wireshark 来查看 PC 的网卡接收和发送的网络数据。